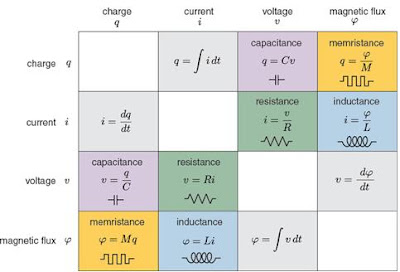

Equations of circuit theory led to a prediction of the memristor almost 40 years before the device was discovered. The equations state relations among four variables: charge (q), current (i), voltage (v) and magnetic flux (phi). Taking these variables in pairs, there are six possible combinations, but only five equations were known

Will the memristor turn out to be a transformative technology, the key to putting hundreds of trillions of devices in the palm of your hand? Or will we be asking, a few years from now, “Whatever happened to the memristor?”

The TiO2 memristor is just one of many contending new technologies. Considering only the realm of switched-resistance memory elements, there are several other candidates, including devices based on phase changes, on magnetic fields and on electron spin. (Chua argues that all these devices should be classified as memristors.) To evaluate the long-term prospects of such technologies, one would have to go beyond basic principles of operation to questions of reliability, longevity, uniformity, cost of manufacturing and dozens of other details.

2. Design considerations for variation tolerant multilevel CMOS/Nano memristor memory

With technology migration into nano and molecular scales several hybrid CMOS/nano logic and memory architectures have been proposed thus far that aim to achieve high device density with low power consumption. The discovery of the memristor has further enabled the realization of denser nanoscale logic and memory systems. This work describes the design of such a multilevel memristor memory (MLMM) system, and the design constraints imposed in the realization of such a memory. In particular, the limitations on load, bank size, number of bits achievable per device, placed by the required noise margin (NM) for accurately reading the data stored in a device are analyzed.

3. An Approach to Tolerate Process Related Variations in Memristor-Based Applications

Memristors have been proposed to be used in a wide variety of applications ranging from neural networks to memory to digital logic. Like other electronic devices, memristors are also prone to process variations. We show that the effect of process induced variations in the thickness of the oxide layer of a memristor has a non-linear relationship with memristance. We analyze the effects of process variation on memristor-based threshold gates. We propose two algorithms to tolerate variations on memristance based on two different constraints. One is used to determine the memristance values for a given list of Boolean functions to tolerate a maximum amount of variation. The other is used to determine the list of Boolean functions that can tolerate a maximum amount of variation for given memristance values. Finally, we analyze the performance of memristor-based threshold gates to tolerate variations.

4. Memristor based programmable threshold logic array

In this work, we utilized memristors in the realization of power and area efficient programmable threshold gates. Memristors are used as weights at the inputs of the threshold gates. The threshold gates are programmed by changing the memristance to enable implementation of different Boolean functions. A new threshold gate-array architecture is proposed and evaluated for power, area and delay metrics. The CAD setup that was utilized in the evaluation of the aforementioned architecture, can also be used to analyse the performance of emerging computing technologies. The proposed architecture achieves an average power reduction of 75% and area (transistor count) reduction of 75% when compared to look-up-table (LUT) based logic with some delay penalty.

5. Design of embedded MRAM macros for memory-in-logic applications

In this article we present a design method for integrating non-volatile MRAM memory cells into standard CMOS design. The emphasis is on standard cell based flow for general purpose logic and automatic generation or MRAM macros suitable for the applications. We present a design space exploration for this purpose and transient simulation results of the hybrid MTJ/CMOS designs. We continue the article with examples of automatic macro generation, integration layout and a prototype in 130nm CMOS which is designed to test a large subset of this design space. In conclusion we show that a high 3D integration density with reasonable speed can be achieved with automatic flow by sharing the reading/writing circuitry among a number of MTJs.

6. Low-power dual-element memristor based memory design

Recently, the emerging memristor device technology has attracted significant research interests due to its distinctive hysteresis characteristic, which potentially can enable novel circuit designs for future VLSI circuits. In particular, characteristics such as non-volatility, non-linearity, low power consumption, and good scalability make memristor one of the most promising emerging memory technologies. Some important design parameter, however, such as speed, energy consumption, and distingushiablility, are mainly determined by the memristor’s physical characteristics. In this paper, a key observation of memristor’s asymmetric energy consumption is made by the detailed analysis of the transient power consumption. Based on this observation, we propose a dual-element memory structure in which each memory cell consists of two memristors. By constantly writing complement bits into the two elements within a cell, the dual-element is flexible to satisfy design constraints which are usually difficult to be satisfied with one-cell memory structure. Design space of the dual-element memory cell is studied and it shows that the trade-offs among the energy, speed, and distingushiablility should be explored for different design objectives. In particular, we show that under the energy-driven optimization, the proposed dual-element memory achieves the same programming speed and distinguishability as conventional single-element memory but the energy consumption can be reduced by up to 80%.

If you liked this article, please give it a quick review on ycombinator or StumbleUpon. Thanks

Brian Wang is a Futurist Thought Leader and a popular Science blogger with 1 million readers per month. His blog Nextbigfuture.com is ranked #1 Science News Blog. It covers many disruptive technology and trends including Space, Robotics, Artificial Intelligence, Medicine, Anti-aging Biotechnology, and Nanotechnology.

Known for identifying cutting edge technologies, he is currently a Co-Founder of a startup and fundraiser for high potential early-stage companies. He is the Head of Research for Allocations for deep technology investments and an Angel Investor at Space Angels.

A frequent speaker at corporations, he has been a TEDx speaker, a Singularity University speaker and guest at numerous interviews for radio and podcasts. He is open to public speaking and advising engagements.